在現代電子設備設計中,電磁兼容性(EMC)問題日益重要,它直接影響到設備的穩定性和可靠性。本文將從電子元器件的選擇和多層電路板設計的角度,探討如何優化設計以提升EMC性能。

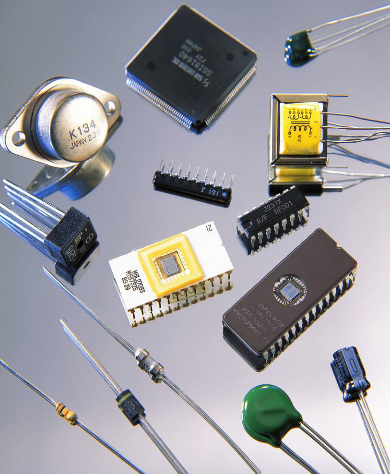

一、電子元器件的選擇

電子元器件的選擇是EMC設計的基礎。以下是關鍵要點:

- 選擇低噪聲元器件:優先選用具有低電磁輻射和抗干擾能力的元器件,例如低噪聲放大器、屏蔽電感等。避免使用高開關頻率或高頻元器件,除非必要,因為它們容易產生電磁干擾(EMI)。

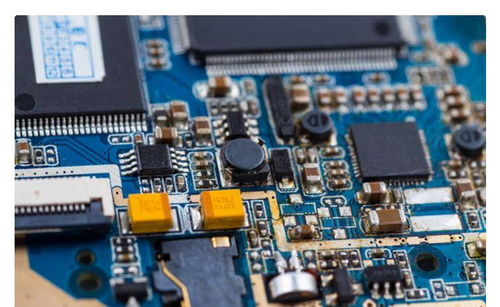

- 注意元器件的封裝和布局:表面貼裝器件(SMD)通常比通孔器件具有更好的EMC性能,因為它們減少了引線長度,從而降低了寄生電感和電容。同時,選擇帶屏蔽的元器件,如屏蔽電感和電容器,可以有效減少輻射。

- 考慮元器件的頻率特性:在高頻應用中,應選擇高頻特性良好的元器件,例如高頻電容和鐵氧體磁珠,以抑制高頻噪聲。注意元器件的自諧振頻率,避免在關鍵頻段產生諧振。

- 使用去耦和旁路電容:在電源引腳附近放置適當的去耦電容(如0.1μF和10μF組合),以濾除高頻噪聲。旁路電容則用于抑制信號線上的干擾。

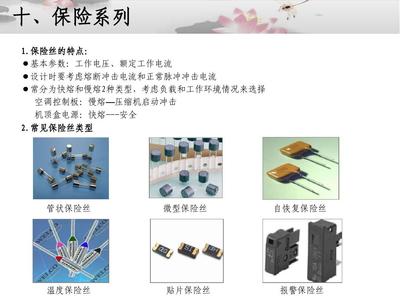

- 選擇抗ESD和浪涌的元器件:在易受靜電放電(ESD)或電源浪涌影響的場合,選用具有內置保護功能的元器件,如TVS二極管,以提高系統的魯棒性。

二、多層電路板設計注意要點

多層電路板設計是EMC優化的核心,良好的布局和布線可以顯著減少干擾。以下是關鍵注意事項:

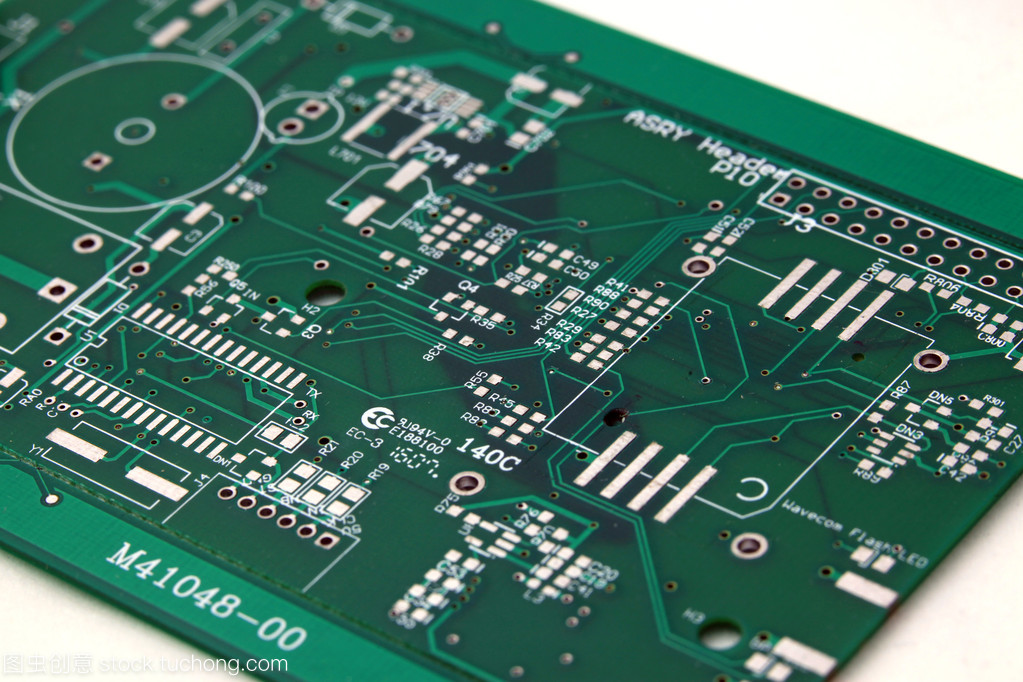

- 分層策略:采用多層板結構,通常包括電源層、接地層和信號層。確保電源和接地層緊密耦合,例如使用相鄰的電源和接地平面,以減少環路面積和阻抗。建議至少使用4層板,其中一層專門用作接地平面。

- 接地設計:實現良好的接地系統是EMC的關鍵。使用單點或多點接地策略,根據頻率和應用場景選擇。在高頻設計中,多點接地更有效,以減少接地回路。確保接地平面連續,避免分割,以提供低阻抗返回路徑。

- 電源分配網絡(PDN)設計:優化電源層布局,使用去耦電容在電源入口和IC附近,以穩定電源電壓并抑制噪聲。注意電源平面的分割,避免不同電源域之間的耦合。

- 信號完整性管理:對于高速信號線,采用阻抗匹配和端接技術,以減少反射和串擾。使用差分對布線來處理敏感信號,并保持信號線短而直,避免長平行走線。

- 屏蔽和隔離:對敏感電路或高頻部分進行屏蔽,例如使用接地覆銅或金屬屏蔽罩。在板上設置隔離區域,將模擬和數字電路分開,以減少交叉干擾。

- 過孔和返回路徑:注意過孔的設計,避免在關鍵信號路徑上使用過多過孔,因為它們可能引入寄生電感。確保每個信號都有明確的返回路徑,通常通過就近的接地過孔實現。

- 測試和驗證:在設計階段進行EMC仿真,并使用原型板進行實際測試,及早發現并解決潛在問題。

EMC設計是一個系統工程,需要從元器件選擇到電路板布局全面考慮。通過優化元器件和多層板設計,可以有效提升電子設備的電磁兼容性,確保其在不同環境下可靠運行。設計者應不斷學習最新標準和技術,以應對日益復雜的EMC挑戰。